你设计的产品,用国产晶振总是不稳定,为什么?是你设计不到位

前言

年轻的硬件屌丝应该都碰到这两种问题:

1, 工程样机阶段生产调试都正常。等到小批量(300pcs以上)的阶段有反馈某些功能不正常,例如系统不启机(系统时钟晶体不起振)、以太网功能不正常(25M/50M晶体不起振)、BT功能不正常(26M晶体不起振),但是数量太少,加上项目催的紧急,更换晶体后都正常了;

2, 市场客户退回设备,晶体电路工作不正常(不起振、起振不稳定、频偏大),更换晶体后都正常了。原创今日头条:卧龙会IT技术

估且都认为是晶体品质问题导致。消费内电子用的国产晶体居多,爱她的性价比但也接受被黑的品质,国产货就替你的设计缺失背锅了。

产品量产了,加上现在的轻资产模式,工厂包工包料出货。到了这个阶段后发现工厂和你不干了,3%以上的不良你得出维修费,这就尴尬了。

数据一分析,排除其他几个加工过程带出的问题,晶体不起振成了大头了。这个锅你得背了,晶体厂家对于晶体有业界标准的测试设备及分析手段,测试通过证实晶体没有问题。

而且再打脸的是,晶体交叉调换下两块板都好了(焊接原因估计你说不出口吧)。

怀疑主芯片有问题,可能性很小(心里也没底气吧),芯片原厂技术及大的代理商可能也不鸟你。当然你也可能幸运点,大客户吗。

晶体厂家FAE和技术人员建议你修改下起振电容、测试下负性阻抗、频偏,或者直接帮你改了电容好了。你敢直接改吗?

心里没底不敢改(万一改出比现在比例还高了、改出频偏大丢包了),量产机型改这种地方说不出个机理1234来,ECN老大不会签字的(这可是产品的心脏部分哦)。怎么破了?

解决方案概述

懒人方案

懒人方案,当然也是一个基本不用动脑几乎无风险的解决方案。唯一带来的问题就是成本上升了(换国外大牌晶体),前提是你的产品还得有一定量和代理商合作有一定基础。

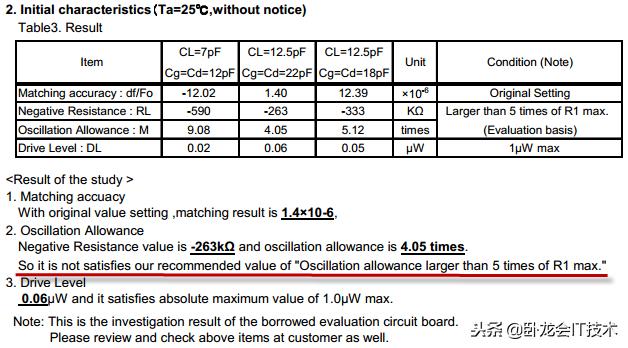

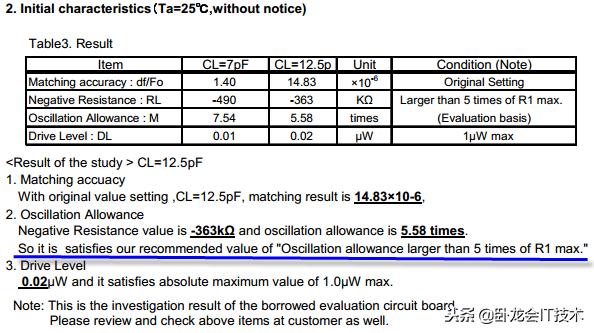

Epson、Sekio等有提供此类电路设计服务,只需通过代理商寄单板到相应厂家技术中心(貌似在上海)去。晶体厂家会按照你的实际设计借助部分测量设备及此领域积累经验,提供一组合理稳定的外设器件(电容、电阻)值和测试报告给你,供后续设计参考。分析周期大概是两周内。

这条路也可以走,但是前提是有量或者能忽悠出量,代理商愿意配合做。不过这样子那硬件工程师还有何颜面了。被骂抄EVM都抄不好,问题还需要晶体厂家帮忙解决。

干货方案

可能很多读者已经受不了,上干货,装逼大家都会。或者再俗点你牛逼你来呀!年轻人,要淡定淡定!其实装逼有时候也挺累的。

认识晶体:

晶体样子

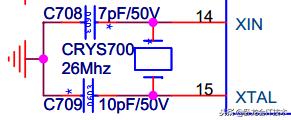

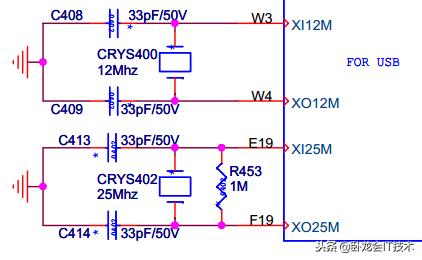

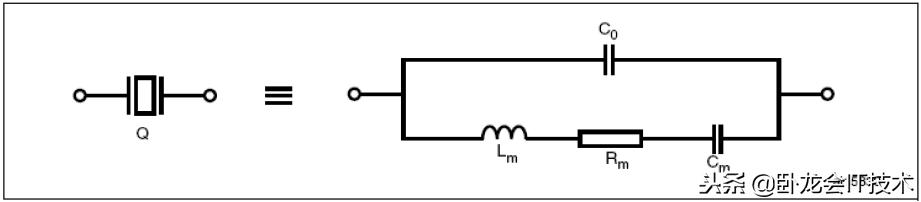

晶体电路符号及晶体等效电路

C0(静电容:Shunt Capacitance):等效电路中与串联臂并接的电容(其值一般与晶体尺寸有关)

Cm(动态等效电容):代表晶体弹性

Lm(动态等效电感):代表晶体机械振动的惯性

Rm(动态等效电阻):代表电路的损耗

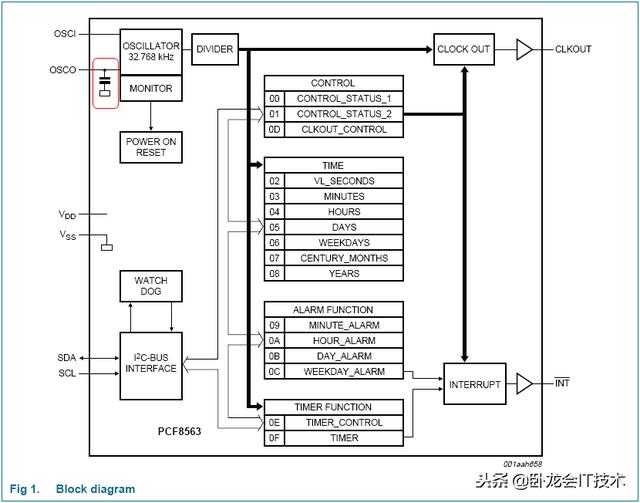

备注:晶体与晶振区别,简单概括晶体是晶振的一部分,晶振包含了晶体及起振电路。

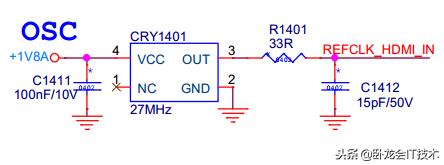

晶振电路设计相对于说简单点,处理好layout、晶振供电、对于晶振输出预留滤波器件解决后续EMI问题就可以了(驱动比较强),对于负性阻抗、频偏、匹配起振电容不涉及。

对于晶体起振本质原理不做介绍了,有兴趣可以参考反馈振荡器相关知识。

正式开始设计

本文完全从一个设计加测试角度考虑,设计出的晶体电路参数符合、稳定可靠的电路来出发。

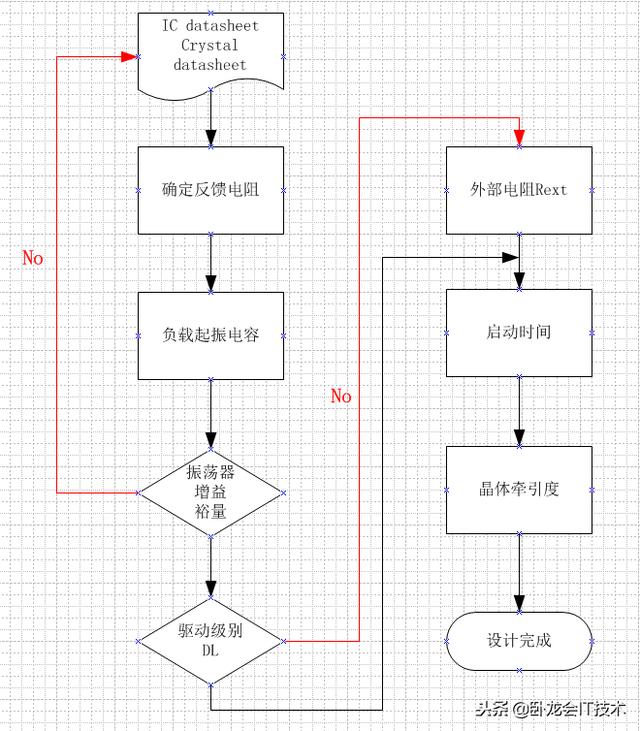

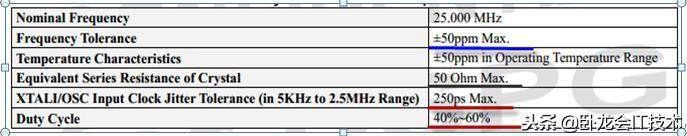

Datasheet整理

1,频偏符合设计(IC规格书要求),原创今日头条:卧龙会IT技术

2,电平符合设计(IC规格书要求)

3,占空比符合设计(基本不存在问题)

4,负性阻抗符合业界要求(业界要求)

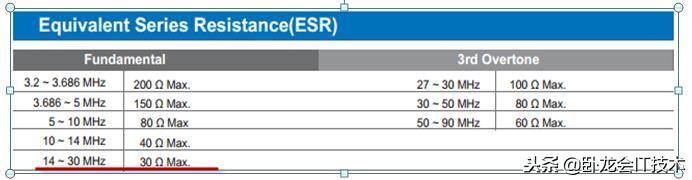

|-R| > 3~5倍ESR(max)

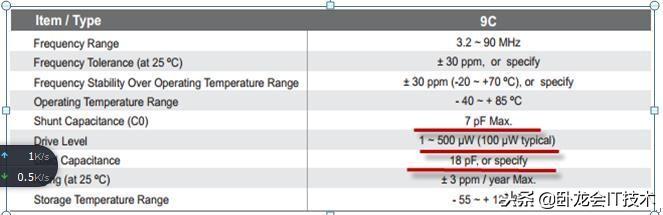

5,驱动功率符合设计(晶体规格书)

6,测试设备

频率计数器(频谱仪),示波器(电压探头+电流探头),可调电阻。

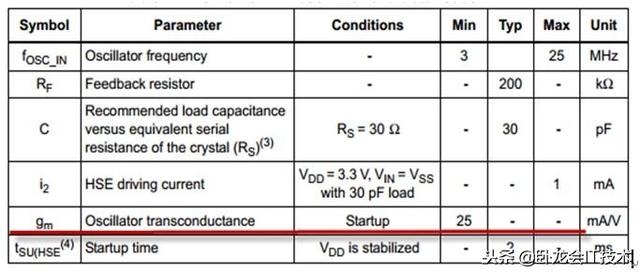

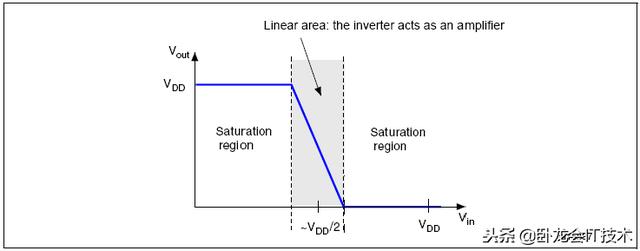

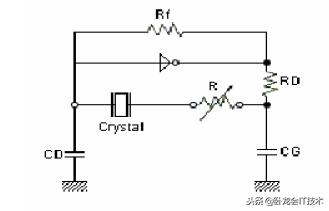

反馈电阻

大多数情况,反馈电阻RF是内嵌在振荡器电路内。作用是通过引入反馈使反相器的功能等同于放大器。Vin和Vout之间增加的反馈电阻使放大器在Vout=Vin时产生偏置,迫使反相器工作在线性区域(下面反向电路工作示总图中阴影区)。

放大器放大了晶体的正常工作区域内的在并联谐振区内的噪声(例如晶体的热噪声),从而引发晶体起振。在某些情况下,如果在起振后去掉反馈电阻RF,振荡器仍可以继续正常工作。

反相器工作示意图

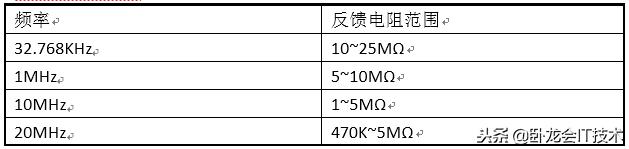

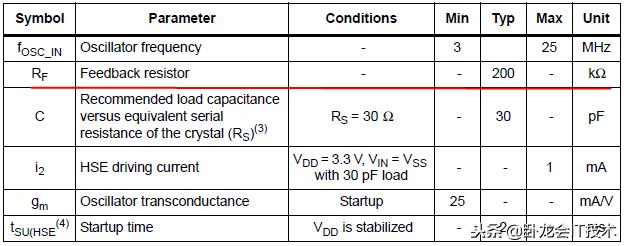

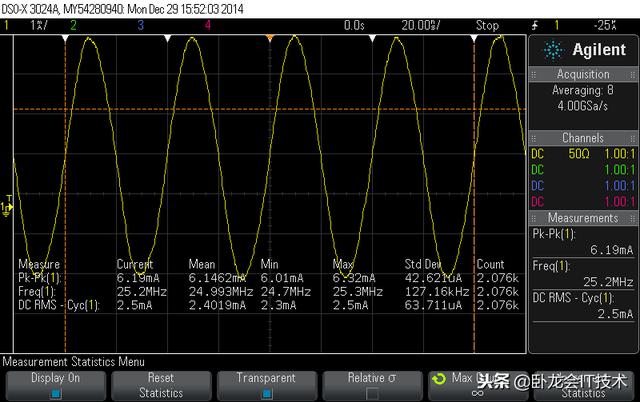

RF典型值如下表:

某IC规格书中RF描述

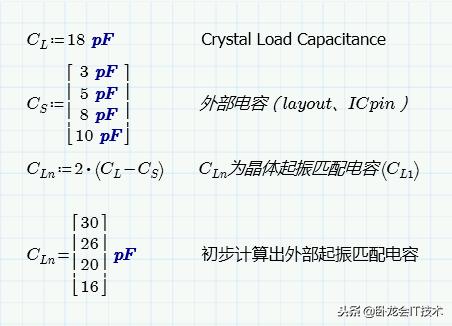

起振电容计算

匹配起振电容初步计算:

CL1=CL2=CLn=16~30pF

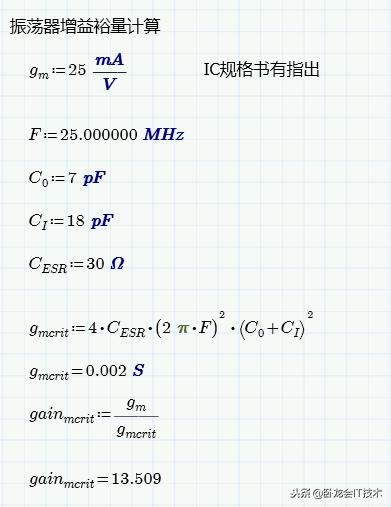

振荡器跨导增益

行业要求:反相器夸导(gm)必须满足:gm > gmcrit。在这种情况下才满足起振的正当条件。为保证可靠的起振,增益裕量的最小值一般设为5。如果IC规格书未提供此值,后续可以测试负性阻抗来替代此步要求。原创今日头条:卧龙会IT技术

驱动级别DL

驱动级别描述了晶体的功耗。晶体的功耗必须限制在某一范围内,否则石英晶体可能会由于过度的机械振动而导致不能正常工作。通常是由晶体制造商给出驱动级别的最大值,超过这个值时,晶体就会受到损害。

驱动级别由下述表达式给出:

DL=ESR * IQ2

其中:ESR是指晶体的等效串联电阻(其值由晶体制造商给出):

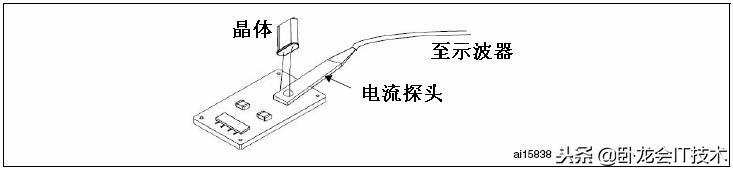

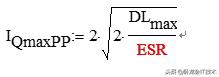

IQ是流过晶体电流的均方根有效值,使用示波器可以观测到其波形为正弦波。电流值可使用峰-峰值(IPP).当使用电流探头时(,示波器的量程比例可能需要设置为1mA/1mV。

如先前所描述,当使用限流电位器调整电流值,可使流过晶体的电流不超过IQMAX均方根有效值(假设流过晶体的电流波形为正弦波)

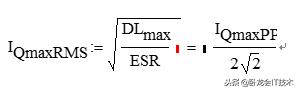

均方根有效值表达式如下:

因此流过晶体的电流IQ不应超过I_QmaxPP

这就是为什么需要外部电阻REXT的原因。当IQ超过IQmaxPP时,REXT是必需的,并且REXT要加入到ESR中去参与计算IQmax。原创今日头条:卧龙会IT技术

IQ怎么来?示波器加电流探头测试了。

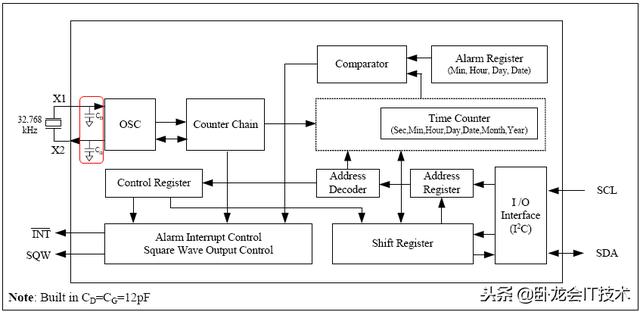

启动时间

启动时间是指振荡器启动并达到稳定所需的时间。这个时间受外部CL1和CL2电容影响,同时它随着晶体频率的增加而减少。

不同种类的晶体对启动时间影响也很大,石英晶体的启动时间比陶瓷晶体的启动时间长得多。起振失败通常和Gainmargin有关,过大或过小的CL1和CL2,以及过大的ESR值均可引起Gainmargin不能满足起振条件。

频率为MHz级的晶体的启动时间是毫秒级的。

而32kHz的晶体的启动时间一般要1~5秒。

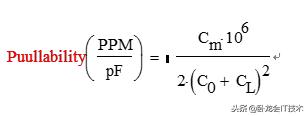

晶体牵引度

晶体的牵引度(译注:也叫可调度)是指工作在正常并联谐振区的晶体频率的变化率。这也用于衡量随负载电容变化而导致的频率变化,负载电容的减少会导致频率的增加,反之负载电容的增加会导致频率的减小。晶体的牵引度表达式如下:

频偏就调这里,不过调完了别忘记喵下其他参数。原创今日头条:卧龙会IT技术

频偏用示波器测试没有问题呀!大哥你确定你不是来逗我玩的,你可以先弄清ppm是怎么来的。

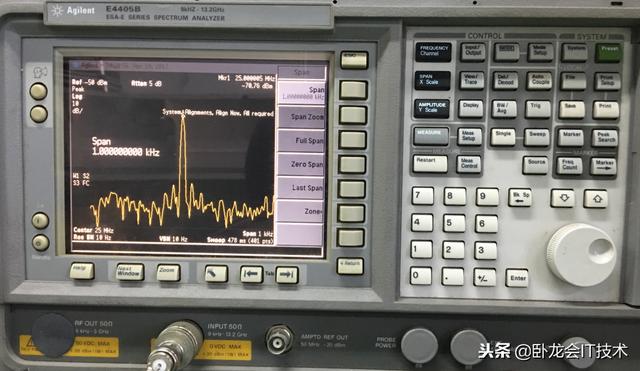

频谱仪测试

频率计数器测试相对于来说更简单,但是测试注意下探头电容影响。频率计数器测试频偏精度要高于频谱仪,特别注意的是频谱仪测试方波精度更差点。

负性阻抗

对于部分芯片规格书或者厂家不能提供gm,此部分可以采用近视负性阻抗来替代增益裕量。

负性阻抗是指从石英晶体谐振器的两个端子往振荡回路看过去,在振荡频率时的阻抗特性值。振荡回路上必须提供足够的放大增益值来补偿石英晶体谐振器在共振时的机械能损失。

负性阻抗并不是晶体谐振器的产品参数,确是振荡电路的一项重要参数。

负性阻抗是用来评价振荡回路质量(Q)的一个重要参数,在某些情形下(例如老化、温度变化、电压变化等),若振荡回路不够好,可能不振荡。

IC的负性阻抗(Negative resistance,-R)测量方式如下

a,串联一电阻(R)至晶体端点(所连IC输出端);

b,调整R值,使晶体由起振至停止振荡;

c,当回路由起振至停止振荡时,测量R值;

d,得到负性阻抗值|-R|=RL+RD,其中

Rr为晶体等效串联电阻。

装完逼深沉总结

晶体电路设计几个重点关注地方:

反馈电阻:搞清楚什么时候该加什么时候不该加。电阻范围比较宽,即使芯片内部预留了,你加了只要不夸张也可以正常使用。

起振匹配电容:理论计算完,实际测试下频偏基本可以确定下来合理值。搞清楚频偏不是用示波器测试出来就基本没有问题了。另外看IC规格书此部分睁大眼睛,有时候下边的坑是自己给自己埋得,而且埋得很深。

负性阻抗:建议设计全部大于5倍,如果3倍都做不到,那就不好意思只能重新选择晶体了。晶体选型并不是简单的看频率、频偏、封装就完事了,CL、ESR等也是你要用到的。

DL/REXT电阻:该留还得留,既然留就得留对,不留说不定哪天就挂在外边了。

你设计的产品,用国产晶振总是不稳定,为什么?是你设计不到位http://t.jinritoutiao.js.cn/8R4BJc/